Ciao a tutti ragazzi, scrivo qui perché c'è un esercizio di elettronica dello stato solido che non riesco a capire molto bene e spero qualcuno possa aiutarmi. Ecco il testo:

In un transistore MOS a canale n, con tensione di soglia VT=0,5 V e tensione tra gate e source VGS=1.2 V (e source connesso al body), viene applicata una tensione tra drain e source di valore:

a) VDS=3V; b) VDS =0,7 V; c) VDS =0,5V.

Disegnare l’andamento qualitativo del potenziale lungo il canale, nei tre casi.

Allora studiando dalle dispense del professore sono arrivato a queste mie conclusioni:

1) A bassi valori di tensione VDS il canale è semplicemente resistivo, cioè presenta una caduta di potenziale linearmente crescente lungo il canale. e questo penso sia riguardo il caso C, visto che la tensione non supera la VT

2) Per valori alti della tensione VDS situò arrivare alla situazione limite

VMS(x) < VT

Ossia localmente il canale scompare perché non si supera la tensione di soglia. Naturalmente questo si verifica quando la tensione di drain vale almeno

VDS- VGS>VT

E questo dovrebbe essere il caso A...

Per il caso di 0,7 cioè di uguaglianza della Vt secondo me c'è semplicemente la formazione del canale e basta, ma soprattutto non capisco il professore che grafico voglia visto che sto impazzendo che sul libro non c'è nulla ( Sedra,Smith), non ne abbiamo uno di stato solido, e ho l'esonero martedì.... Vi ringrazio moltissimo. Ciao!!

2 messaggi

• Pagina 1 di 1

Re: Elettronica dello stato solido. Transistore MOS

Per il caso c) è come hai detto tu, il potenziale di canale (che indico con $V(y)$, $0<y<L$ è la coordinata spaziale) sale quasi linearmente da $V_S = 0$ a $V_D = 0.5V$.

Nel caso b) hai $V_{DS} = V_{DS}^{sat}= V_{GS} - V_T$, che per il MOSFET a canale lungo è la condizione tale per cui il transistore è al bordo tra la zona ohmica e quella di saturazione. In questa condizione il canale superficiale scompare al lato drain (pinch-off). Perché sia mantenuta la continuità di corrente (che tra l'altro è massima in regione di saturazione a fissata $V_{GS}$), il campo elettrico deve presentare una singolarità, ovvero si deve avere

\(\displaystyle \frac{\text{d} V}{\text{d} y} = \infty \)

per $y = L$. Puoi quindi immaginare come sia fatto il potenziale nel caso b): partirà da $0V$ al source e crescerà fino a valere $V_{DS}^{sat}$ al drain, dove la sua tangente (associata al campo elettrico) è verticale.

Nel caso a) hai $V_{DS} > V_{DS}^{sat}= V_{GS} - V_T$, quindi il MOSFET opera in regione di saturazione. Il punto di pinch-off del canale si è spostato indietro rispetto al caso precedente, e in questo punto il potenziale rimarrà a tangente verticale.

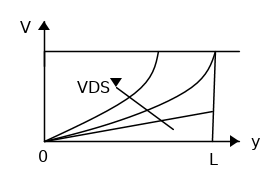

La figura sotto riassume i tre casi (perdona la qualità del mio disegno):

A dirla tutta, si può dimostrare che la forma analitica del potenziale è:

\(\displaystyle V(y) = V_{GS} - V_T + \sqrt{(V_{GS}-V_T)^2 -2 \frac{y}{L}(V_{GS}-V_T) V_{DS} + \frac{y}{L}V_{DS}^2}\),

quindi il potenziale è a forma di parabola.

Un punto che spesso genera confusione: cosa significa che il canale scompare nel punto di pinch-off?

Se il canale scomparisse del tutto il transistore non potrebbe condurre. Quello che scompare è il canale superficiale. Dopo il punto di pinch-off, gli elettroni continuano comunque a viaggiare verso il drain, ma sono spinti lontano dall'interfaccia con l'ossido. Questo perché la componente di campo elettrico in direzione source-drain cambia molto più rapidamente di quella in direzione verticale (del resto abbiamo visto che idealmente il campo è infinito al pinch-off), e si rompe la cosiddetta approssimazione a canale graduale. Per trovare il profilo dei portatori oltre il pinch-off è necessaria un'analisi 2D che credo per ora ti interessi in maniera assai limitata. Il concetto però è che l'approssimazione è valida fino al pinch-off, e ai fini della conduzione (ovvero della corrente portata dal transistor) non ti interessa sapere la distribuzione spaziale dei portatori dopo il pinch-off, perché tanto la corrente si deve conservare.

Spero chiaro.

Nel caso b) hai $V_{DS} = V_{DS}^{sat}= V_{GS} - V_T$, che per il MOSFET a canale lungo è la condizione tale per cui il transistore è al bordo tra la zona ohmica e quella di saturazione. In questa condizione il canale superficiale scompare al lato drain (pinch-off). Perché sia mantenuta la continuità di corrente (che tra l'altro è massima in regione di saturazione a fissata $V_{GS}$), il campo elettrico deve presentare una singolarità, ovvero si deve avere

\(\displaystyle \frac{\text{d} V}{\text{d} y} = \infty \)

per $y = L$. Puoi quindi immaginare come sia fatto il potenziale nel caso b): partirà da $0V$ al source e crescerà fino a valere $V_{DS}^{sat}$ al drain, dove la sua tangente (associata al campo elettrico) è verticale.

Nel caso a) hai $V_{DS} > V_{DS}^{sat}= V_{GS} - V_T$, quindi il MOSFET opera in regione di saturazione. Il punto di pinch-off del canale si è spostato indietro rispetto al caso precedente, e in questo punto il potenziale rimarrà a tangente verticale.

La figura sotto riassume i tre casi (perdona la qualità del mio disegno):

A dirla tutta, si può dimostrare che la forma analitica del potenziale è:

\(\displaystyle V(y) = V_{GS} - V_T + \sqrt{(V_{GS}-V_T)^2 -2 \frac{y}{L}(V_{GS}-V_T) V_{DS} + \frac{y}{L}V_{DS}^2}\),

quindi il potenziale è a forma di parabola.

Un punto che spesso genera confusione: cosa significa che il canale scompare nel punto di pinch-off?

Se il canale scomparisse del tutto il transistore non potrebbe condurre. Quello che scompare è il canale superficiale. Dopo il punto di pinch-off, gli elettroni continuano comunque a viaggiare verso il drain, ma sono spinti lontano dall'interfaccia con l'ossido. Questo perché la componente di campo elettrico in direzione source-drain cambia molto più rapidamente di quella in direzione verticale (del resto abbiamo visto che idealmente il campo è infinito al pinch-off), e si rompe la cosiddetta approssimazione a canale graduale. Per trovare il profilo dei portatori oltre il pinch-off è necessaria un'analisi 2D che credo per ora ti interessi in maniera assai limitata. Il concetto però è che l'approssimazione è valida fino al pinch-off, e ai fini della conduzione (ovvero della corrente portata dal transistor) non ti interessa sapere la distribuzione spaziale dei portatori dopo il pinch-off, perché tanto la corrente si deve conservare.

Spero chiaro.

-

elgiovo - Cannot live without

- Messaggio: 2760 di 3602

- Iscritto il: 24/12/2005, 13:11

- Località: Boise, ID

2 messaggi

• Pagina 1 di 1

Chi c’è in linea

Visitano il forum: Nessuno e 1 ospite